Servizi di Fabbricazione Elettronica One-stop, vi aiutanu à ottene facilmente i vostri prudutti elettronichi da PCB è PCBA

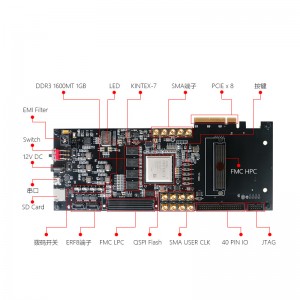

FPGA Xilinx K7 Kintex7 Comunicazione in fibra ottica PCIe

- DDR3 SDRAM: 16 GB DDR3 64 bit bus, velocità di trasmissione dati 1600 Mbps

- QSPI Flash: Un pezzu di QSPIFLASH di 128 mbit, chì pò esse adupratu per i fugliali di cunfigurazione FPGA è u almacenamentu di dati di l'utilizatori.

- Interfaccia PCLEX8: L'interfaccia standard PCLEX8 hè aduprata per cumunicà cù a cumunicazione PCIE di a scheda madre di l'urdinatore. Supporta u standard PCI, Express 2.0. A velocità di cumunicazione à un canale pò ghjunghje sin'à 5 Gbps.

- Porta seriale USB UART: Una porta seriale, da cunnette à u PC attraversu u cavu miniusb per eseguisce a cumunicazione seriale

- Carta Micro SD: Sede di carta Microsd finu in fondu, pudete cunnette a carta Microsd standard

- Sensore di temperatura: un chip di sensore di temperatura LM75, chì pò monitorà a temperatura ambientale intornu à a scheda di sviluppu

- Portu d'estensione FMC: un FMC HPC è un FMCLPC, chì ponu esse cumpatibili cù diverse carte d'espansione standard

- Terminale di cunnessione à alta velocità ERF8: 2 porte ERF8, chì supportanu a trasmissione di signali à ultra alta velocità Estensione 40pin: riservata una interfaccia IO di estensione generale cù 2,54 mm 40pin, O efficace hà 17 coppie, supporta 3,3 V

- A cunnessione periferica di u livellu è di u livellu 5V pò cunnette i periferichi periferichi di diverse interfacce 1O di usu generale.

- Terminale SMA; 13 teste SMA placcate in oru di alta qualità, chì hè cunveniente per l'utilizatori per cooperà cù carte d'espansione AD/DA FMC d'alta velocità per a raccolta è l'elaborazione di u signale

- Gestione di l'orologio: Fonte multi-clock. Quessi includenu a fonte di clock differenziale di u sistema 200MHz SIT9102

- Oscillazione à cristallu differenziale: cristallu 50MHz è chip di gestione di l'orologio programmabile SI5338P: ancu dotatu di

- EMCCLK 66MHz. Pò adattassi accuratamente à diverse frequenze di clock d'usu

- Portu JTAG: 10 punti di sutura Portu JTAG standard di 2,54 mm, per u scaricamentu è u debugging di prugrammi FPGA

- Chip di monitoraghju di tensione sub-reset: un pezzu di chip di monitoraghju di tensione ADM706R, è u buttone cù u buttone furnisce un signale di reset globale per u sistema

- LED: 11 luci LED, indicanu l'alimentazione di a carta di bordu, signale config_done, FMC

- Indicatore di putenza è 4 LED d'utilizatore

- Chjave è interruttore: 6 chjavi è 4 interruttori sò buttoni di reset FPGA,

- U buttone di u prugramma B è 4 chjave d'utilizatore sò cumposti. 4 interruttori à doppia lancia à un cultellu unicu

Scrivite u vostru missaghju quì è mandateci lu

Categurie di prudutti

-

Telefunu

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype