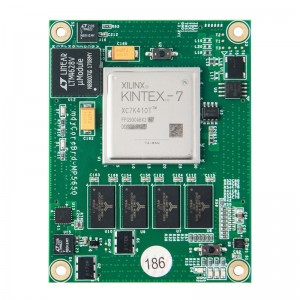

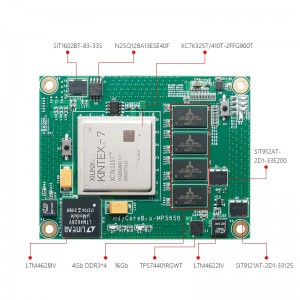

FPGA XILINX-K7 KINTEX7 XC7K325 410T di qualità industriale

DDR3 SDRAMQ: 16GB DDR3, 4GB per pezzu, 16bit Data Bit Data Bid SPI Flash: Un pezzu di 128MBITQSPIFLASH, chì pò esse adupratu per i fugliali di cunfigurazione FPGA è u almacenamentu di dati di l'utilizatori Livelli d'interfaccia FPGA Bank: regulabile 1.8V, 2.5V, 3.3V elettricu Sè avete bisognu di rimpiazzà u livellu, basta à rimpiazzà a pusizione currispundente di a perla magnetica per ottene a regulazione. Alimentazione di a scheda core: gamma 5V-12V di alimentazione EEPROM; M24C02-WMN6TP hè basatu annantu à u dispusitivu di bus I2C. Seguendu u metudu di avviu di a scheda core di u protocolu di seconda linea: supporta dui modi di avviu, chì sò connettori Flash JTAG, QSPI. Portu allargatu, 120pin, interfaccia SFP di a piastra inferiore Panasonic AXK5A2137yg MP5700: 2 moduli ottici ponu ottene una cumunicazione in fibra ottica à alta velocità, finu à 6GB/s. Clock di a piastra inferiore: 1 clock di riferimentu di 200MHz cunnessu à a scheda core. Pede di u tubu di clock MRCC, 1 Pede di u tubu di clock GTX di 125MHz. A piastra inferiore di u clock chì si cunnetta à a scheda core hè un portu di espansione di 40 pin: riservate un portu di estensione di 40 colpi cù una spaziatura standard di 2,54 mm, chì hè adupratu per cunnette u modulu di cuncepimentu di u cliente. Clock di a scheda Essence Core: ci sò parechje fonti di clock nantu à a scheda. Queste includenu u clock di sistema di 200MHz, u clock GTX di 125MHz è u clock EMCCLK di 66MHz. Portu JTAG: 10 punti Portu JTAG standard di 2,54 mm, per scaricà è debugging LED per i prugrammi FPGA: un totale di 6 luci LED rosse in a scheda principale, chì indicanu l'alimentazione di a carta di a scheda, 4 luci indicatrici di signale è i pedi di u tubu IO FPGA sò cunnessi direttamente. Chjave: 4 chjavi. 4 chjavi. Sò i buttoni di reset FPGA, i chjavi Program_b è duie chjavi d'utilizatore.

U FPGA Xilinx-K7 Kintex7 XC7K325 410T hè un mudellu specificu di FPGA (Field-Programmable Gate Array) sviluppatu da Xilinx. Eccu alcuni dettagli chjave nantu à questu FPGA: Serie: Kintex-7: I FPGA di a serie Kintex-7 di Xilinx sò cuncepiti per applicazioni ad alte prestazioni è offrenu un bon equilibriu trà prestazioni, putenza è prezzu. Dispositivu: XC7K325: Questu si riferisce à u dispositivu specificu in a serie Kintex-7. L'XC7K325 hè una di e varianti dispunibili in questa serie, è offre certe specifiche, cumprese a capacità di e cellule logiche, e fette DSP è u conteggio I/O. Capacità logica: L'XC7K325 hà una capacità di cellule logiche di 325.000. E cellule logiche sò blocchi di custruzzione programmabili in un FPGA chì ponu esse cunfigurati per implementà circuiti è funzioni digitali. Fette DSP: E fette DSP sò risorse hardware dedicate in un FPGA chì sò ottimizzate per i compiti di trasfurmazione di signali digitali. U numeru esattu di fette DSP in l'XC7K325 pò varià secondu a variante specifica. Conteggio I/O: U "410T" in u numeru di mudellu indica chì l'XC7K325 hà un totale di 410 pin I/O di l'utente. Questi pin ponu esse aduprati per interfaccià si cù dispositivi esterni o altri circuiti digitali. Altre Caratteristiche: L'XC7K325 FPGA pò avè altre caratteristiche, cum'è blocchi di memoria integrati (BRAM), transceiver à alta velocità per a cumunicazione di dati è varie opzioni di cunfigurazione. Hè impurtante nutà chì i FPGA cum'è u Xilinx-K7 Kintex7 XC7K325 sò dispositivi programmabili chì permettenu di implementà circuiti è funzionalità digitali persunalizati programendu e so cellule logiche. Questa flessibilità li rende adatti per una vasta gamma di applicazioni, cumprese l'informatica ad alte prestazioni, l'elaborazione di segnali digitali è l'accelerazione hardware.

Categurie di prudutti

-

Telefunu

-

E-mail

-

Whatsapp

-

Skype

-

Skype

-

Skype